自製 CPU 實錄:從模擬環境走向硬體實作的挑戰

我分享了將模擬的 8 位元 CPU 設計轉化為實體硬體時那種令人謙卑的經驗,並詳細記錄了在原型製作階段遇到的各種技術障礙與錯誤。

背景

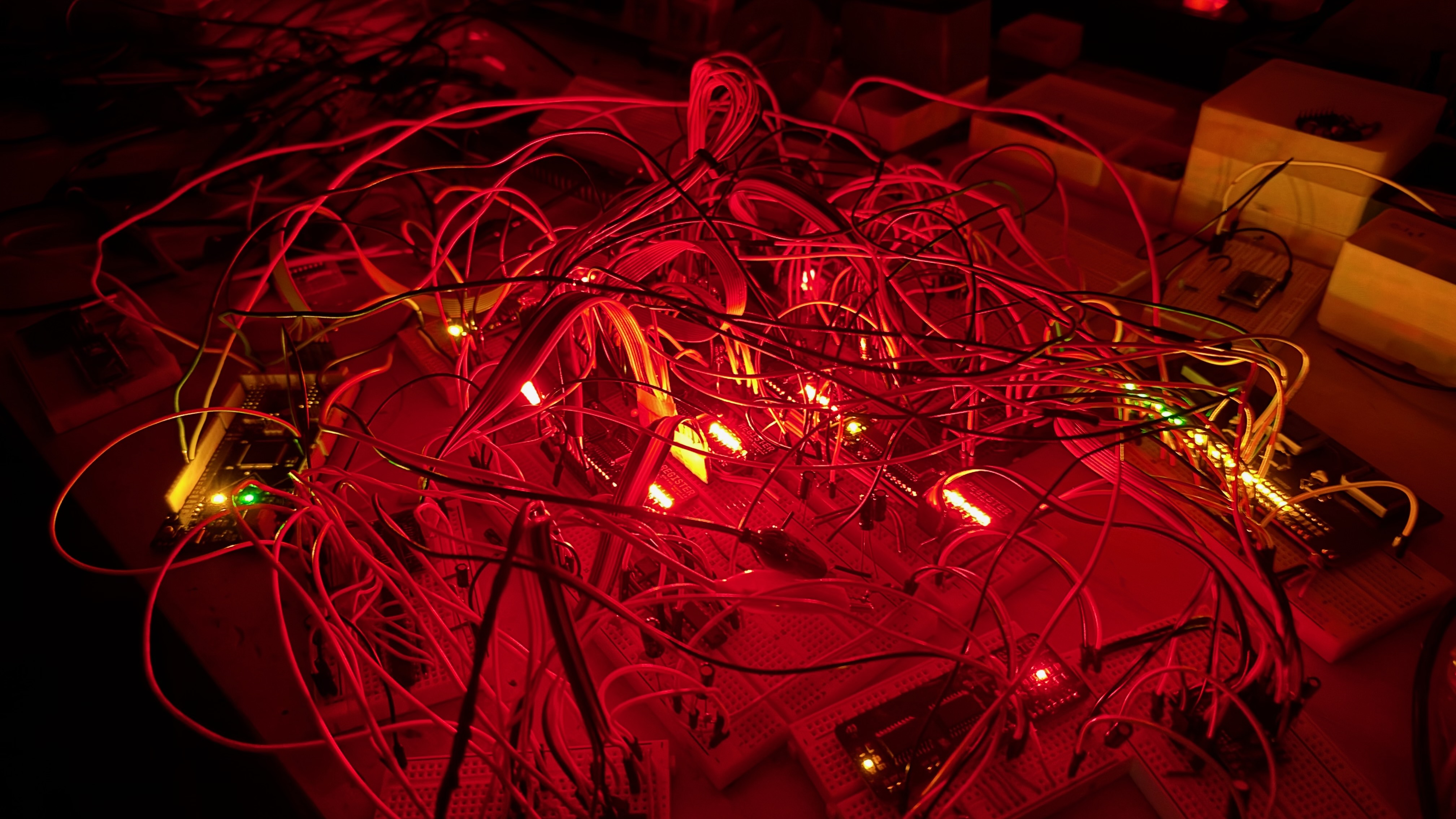

本文是開發者 Will Warren 打造自製 8 位元電腦 WCPU-1 系列文章的第三部分,記錄了他將 Logisim 模擬設計轉化為實體硬體的過程。作者分享了在原型開發階段遭遇的種種挑戰,包括 SMT 零件與麵包板的不相容性、EEPROM 燒錄器的設計缺陷,以及從模擬環境跨越到現實物理世界時所面臨的技術落差。

社群觀點

針對作者從模擬轉向實體硬體的挑戰,Hacker News 的討論呈現出兩種截然不同的技術哲學。部分資深開發者強烈建議愛好者應盡可能留在模擬環境或使用 FPGA,而非執著於實體晶片與麵包板。這類觀點認為,將設計實體化往往會將原本充滿樂趣的架構設計,轉化為處理時序問題、接觸不良、半損壞晶片或雜訊干擾等枯燥且瑣碎的除錯工作。除非目的是為了創造如繼電器電腦般的「藝術聲明」,否則實體建構的過程往往會消磨掉對電腦架構探索的熱情。

然而,另一派意見則認為「樂趣」的定義因人而異,物理世界的限制與挑戰正是某些開發者的動力來源。有留言指出,並非所有人都喜歡 Verilog 等硬體描述語言,且部分 FPGA 廠商的技術文件品質參差不齊,反而增加了進入門檻。對這些開發者而言,處理現實中的物理細節雖然辛苦,卻是一種更具成就感的體驗。這種爭論也延伸到了教育層面,有討論提到早期的電腦架構課程甚至允許學生將設計送往晶圓廠流片,雖然過程艱辛,但這種從無到有的實踐過程具有不可替代的教育價值。

此外,討論串也觸及了電腦發展史中的「雞生蛋、蛋生雞」問題。當讀者好奇第一代 CPU 是如何被程式化時,社群成員補充了歷史背景:在 EEPROM 或現代燒錄工具出現之前,最早期的電腦是透過物理性的重新佈線來變更程式指令。這種從「手動佈線」進化到「微碼燒錄」的過程,正是自製 CPU 愛好者在實作中所能體會到的技術演進縮影。整體而言,社群對於實體建構雖有「吃力不討好」的警示,但仍對這種硬核的實踐精神給予高度評價。

延伸閱讀

在討論中,有留言者分享了其自製的繼電器 CPU 專案(Relay CPU),展示了另一種極致的實體化硬體設計方向。此外,BMOW(Big Mess o' Wires)也是社群中經常被提及的經典自製 CPU 參考案例,適合對實體佈線與硬體除錯有興趣的讀者深入研究。